当英伟达Blackwell架构B200芯片的AI算力达到20 PFLOPS(FP4精度),较H100实现5倍性能跃升时,很多人以为这是3nm制程的功劳——实则先进封装才是幕后功臣。台积电CoWoS封装与HBM3E内存的“零距离”互联,结合英伟达Chiplet设计,让B200的带宽提升至4.8TB/s,延迟降低70%,这才是算力倍增的核心密码。在芯片制程逼近物理极限的今天,先进封装正从“辅助工艺”升级为“算力放大器”,彻底改写行业的性能规则。

一、核心逻辑:破解内存与功耗的双重枷锁

先进封装改写算力规则的核心,是通过缩短互联距离、提升互联密度,同时突破两大行业瓶颈:

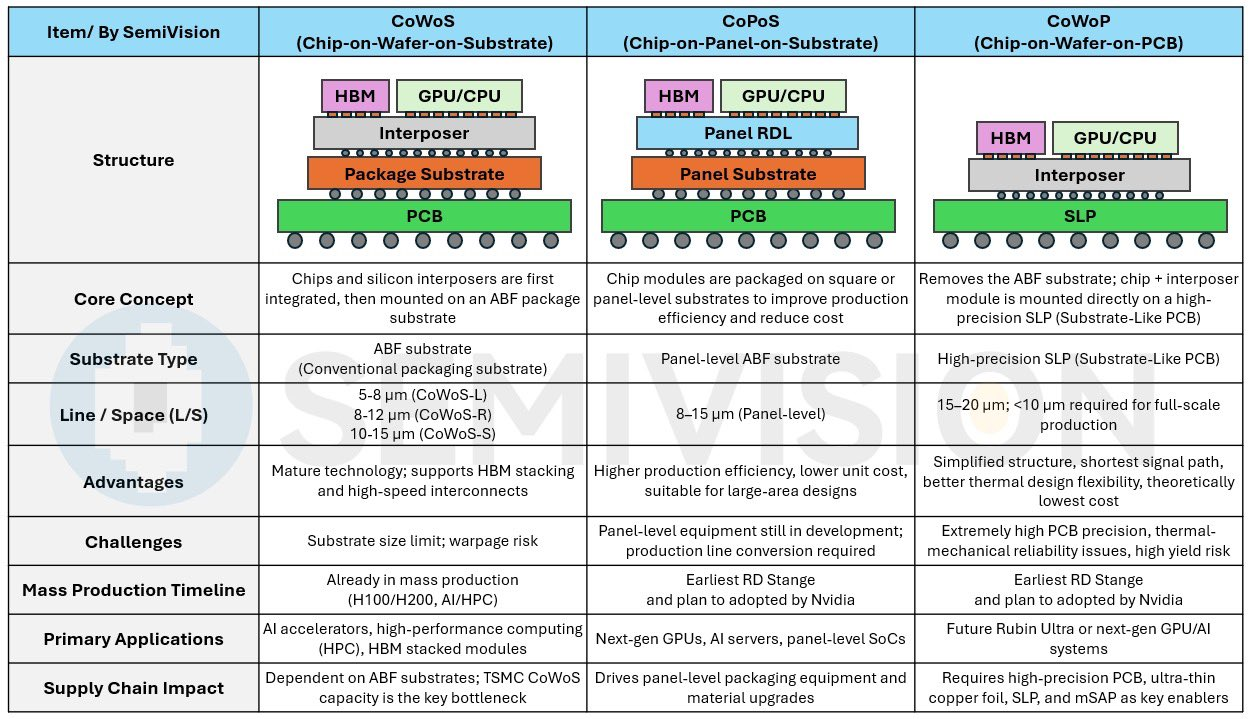

传统封装中,逻辑芯片与内存通过引线键合连接,数据传输距离长达毫米级,形成“内存墙”——GPU算力再强,也受制于内存数据供给速度。而CoWoS封装+硅中介层技术,将HBM内存与GPU核心的互联距离缩短至微米级,带宽提升4-8倍,完美匹配AI芯片的海量数据吞吐需求。

更具突破性的是3D堆叠与混合键合技术:

英特尔Foveros技术将不同功能芯粒垂直堆叠,互联距离从微米级缩短至纳米级,功耗降低40%,最新Xeon Max处理器在同等功耗下算力提升2.5倍;

混合键合(Cu-Cu直接键合) 替代传统凸点互联,互联密度提升10-100倍,间距已达1-2μm,为“芯片即系统”奠定基础;

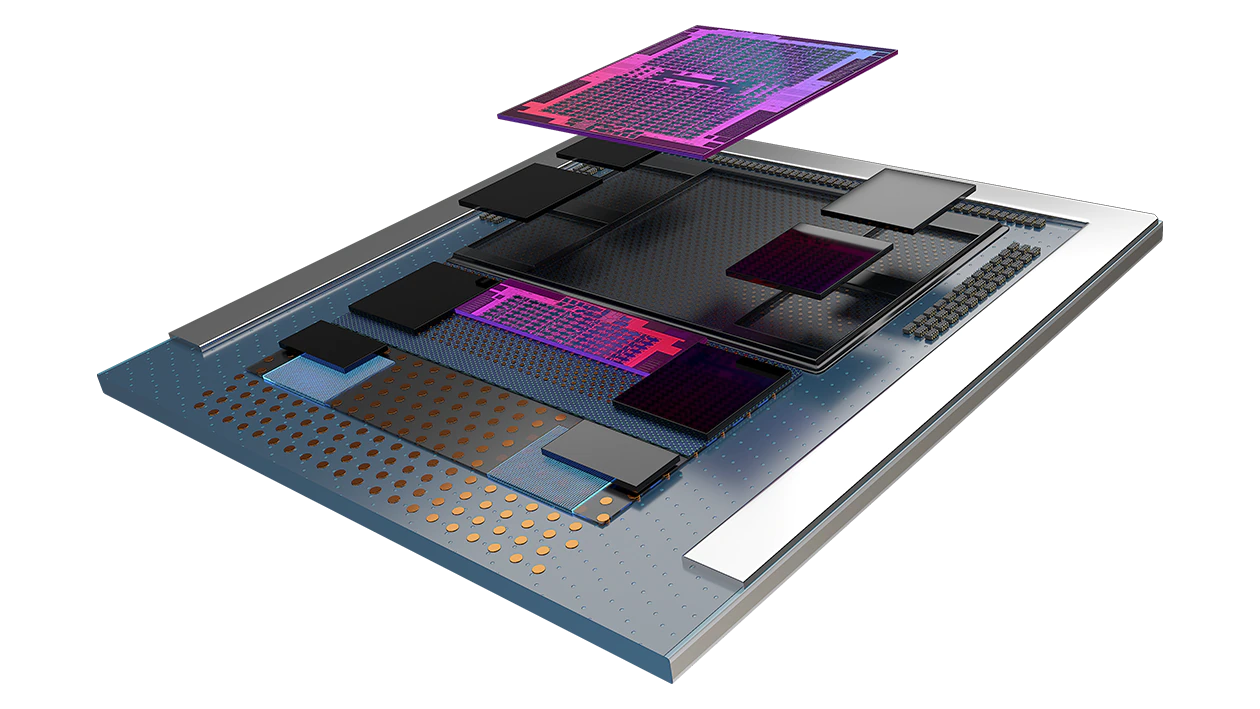

台积电SoIC技术实现芯粒间0.4μm键合,使B200的Chiplet互联延迟降低至亚纳秒级。

2025年最新进展:碳化硅中介层正进入商用阶段,导热率提升5倍,使GPU结温降低20-30℃,散热成本降低30%,防止芯片因过热降频,保证算力稳定输出。

二、算力革命:封装与设计的“协同进化”

算力提升的背后,是封装与芯片设计的“协同革命”——过去封装是“后端环节”,如今已前置到设计阶段,形成“设计-封装-测试”一体化流程。

1. Chiplet设计+先进封装:算力倍增的黄金组合

AMD MI300X:采用“8个GPU芯粒+6个HBM3芯粒”的Chiplet架构,配合台积电CoWoS封装,在3nm工艺下实现8倍性能提升,HBM带宽达5.2TB/s

英伟达Blackwell Ultra:通过Chiplet技术将3nm GPU芯粒与HBM3E内存垂直堆叠,推理性能较H100提升10倍,训练性能提升5倍,功耗降低40%

壁仞科技BR100:自主研发Chiplet互联协议,结合长电科技CoWoS封装,在AI训练任务中实现3倍能效比提升

2. AI驱动的封装设计优化

2025年,AI辅助封装设计成为行业标配:

ML模型可快速探索数百万种芯粒排列与互联配置,将设计时间从数周缩短至数天

自动预测热分布与信号完整性,优化功耗与性能平衡

预测良率风险,降低先进封装的制造成本

三、成本重构:先进封装如何降低“算力门槛”

先进封装不仅提升性能,更在重构算力成本逻辑:

采用3nm制程制造一颗全尺寸AI芯片,成本超过8000美元,而通过Chiplet技术,将核心算力芯粒用3nm制程,外围I/O、存储控制器等芯粒用28nm成熟制程,整体成本可降低40%以上。更重要的是,先进封装大幅提升良率——单芯片良率50%的情况下,采用4个芯粒的Chiplet方案,整体良率可提升至93.75%。

四、场景分化:不同算力需求的封装“最优解”

先进封装的算力放大效应在不同场景呈现差异化,2025年已形成明确的技术路线选择:

1. AI训练场景:CoWoS+3D堆叠+混合键合(算力“核弹”组合)

标配:英伟达B200、AMD MI300X、谷歌TPU v5e均采用此组合

最新突破:台积电推出CoWoS Ultra技术,支持单封装集成12个HBM4内存堆栈+4个3D堆叠芯片系统,性能提升3.5倍,满足万亿参数大模型训练需求

散热创新:碳化硅中介层使GPU结温降低20-30℃,散热成本降低30%,保证芯片稳定输出峰值算力

2. 边缘计算场景:WLP+扇出型封装(体积与功耗优先)

晶圆级封装(WLP):体积缩小60%、功耗降低35%,完美适配AI眼镜、人形机器人等终端设备

扇出型封装(FO-WLP):集成无源元件,降低系统成本,已成为自动驾驶域控制器的主流选择

最新进展:万有引力电子发布的空间计算MR芯片,采用WLP封装,彩色透视延迟低至9毫秒,打破世界纪录

3. 自动驾驶场景:Chiplet+异构集成(灵活组合算力)

优势:可根据自动驾驶级别(从L2到L5)灵活组合算力芯粒、传感器芯粒和安全控制芯粒

最新应用:特斯拉HW4.0采用“7nm FSD芯粒+28nm传感器接口芯粒”的Chiplet方案,算力提升3倍,成本降低40%

安全保障:通过芯粒级冗余设计,提升自动驾驶系统的可靠性

五、未来演进:迈向“极致集成”的算力新纪元

2025-2026年,先进封装将向三大方向演进,进一步释放算力潜力:

1. 材料革命:突破硅基限制

玻璃基板封装:介电性能优于硅中介层,支持更高频率信号传输,台积电已进入量产验证阶段,预计2026年商用,可提升带宽2倍,功耗降低25%

碳化硅中介层:解决超大芯片散热难题,结温降低20-30℃,已在英伟达Blackwell Ultra中测试应用

有机-无机混合基板:平衡成本与性能,适合中高端AI芯片批量生产

2. 3D堆叠极限:层数突破+全功能集成

堆叠层数:从目前的4-6层提升至10-12层,实现“逻辑-存储-射频-传感器”的全功能集成

混合键合间距:从目前的1-2μm缩小至0.5μm以下,互联密度提升4倍

Chiplet+3D堆叠融合:先横向扩展,再垂直堆叠,实现“无限算力”的模块化扩展

3. 封装与系统协同:从“芯片封装”到“系统封装”

光电共封装(CPO):将光学引擎与AI芯片集成在同一封装中,带宽提升10倍,功耗降低50%,已在英伟达Blackwell平台中应用

液冷封装一体化:将散热系统集成到封装设计中,解决超大规模AI芯片(>1000W)的散热难题

芯粒即插即用:标准化互联接口,实现不同厂商芯粒的混合集成,加速AI芯片开发周期

六、时代已至:封装定义算力的产业新规

2025年数据显示,先进封装市场规模已达180亿美元,预计2026年将突破250亿美元。对于企业而言,布局先进封装已不是“选择题”而是“必修课”——谁能掌握“封装定义算力”的核心能力,谁就能在AI时代的算力竞争中占据主导地位。

关键趋势:

台积电:2025年底将CoWoS产能提升50%,满足Blackwell Ultra和下一代Rubin架构需求;

英特尔:Foveros技术将支持21,000mm²超大规模封装,突破单封装硅片集成极限;

三星:2026年推出混合键合+玻璃基板的“终极封装方案”,性能提升4倍,成本降低50%;

国产封装企业:长电科技、通富微电等加速CoWoS与混合键合技术研发,2025年已实现2.5D封装的批量生产。

当摩尔定律放缓,先进封装正成为AI算力突破的新引擎。从H100到B200,从3倍到10倍的算力跃升,我们见证的不仅是技术的进步,更是一场由先进封装引领的“算力革命”——这场革命才刚刚开始,未来5年,AI芯片算力有望再翻20倍,彻底改变人类与AI的交互方式。