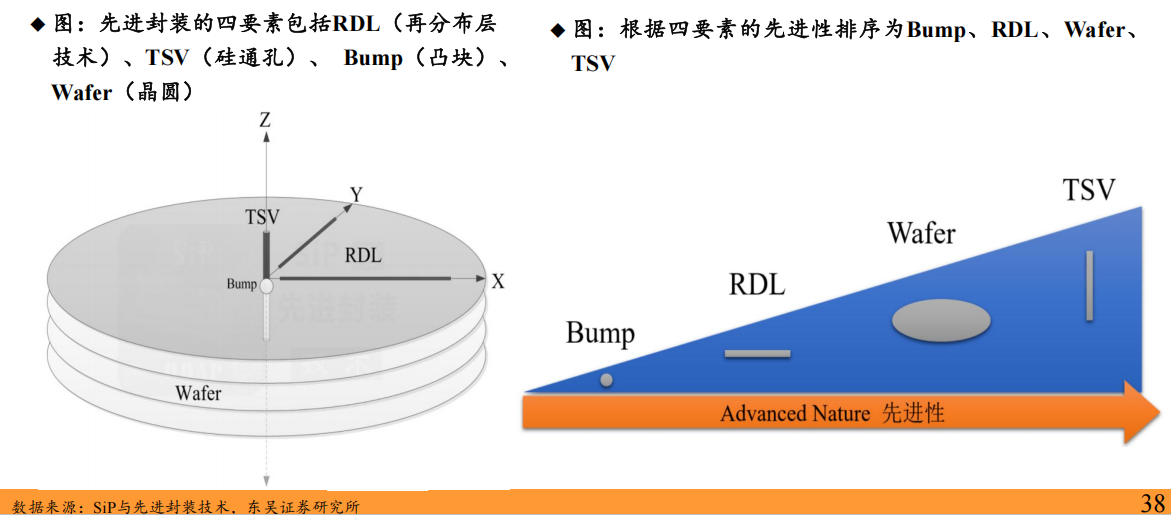

先进封装与传统封装的核心区别在于芯片与外部系统的电气连接方式:先进封装摒弃了传统的引线连接,转而采用传输速度更快的凸块、中介层等结构。构成先进封装的四个关键要素包括再分布层(RDL)、硅通孔(TSV)、凸块(Bump)和晶圆(Wafer)。任何封装技术只要具备其中至少一个要素,即可归类为先进封装。在这四个要素中,RDL负责XY平面内的电气延伸,TSV实现Z轴方向的电气互联,Bump承担界面连接与应力缓冲功能,而Wafer则作为集成电路的载体,同时为RDL和TSV提供介质和基底。

以下将重点探讨凸块(Bump)、倒装(Flip Chip)、再分布层(RDL)及硅通孔(TSV)四项关键技术。

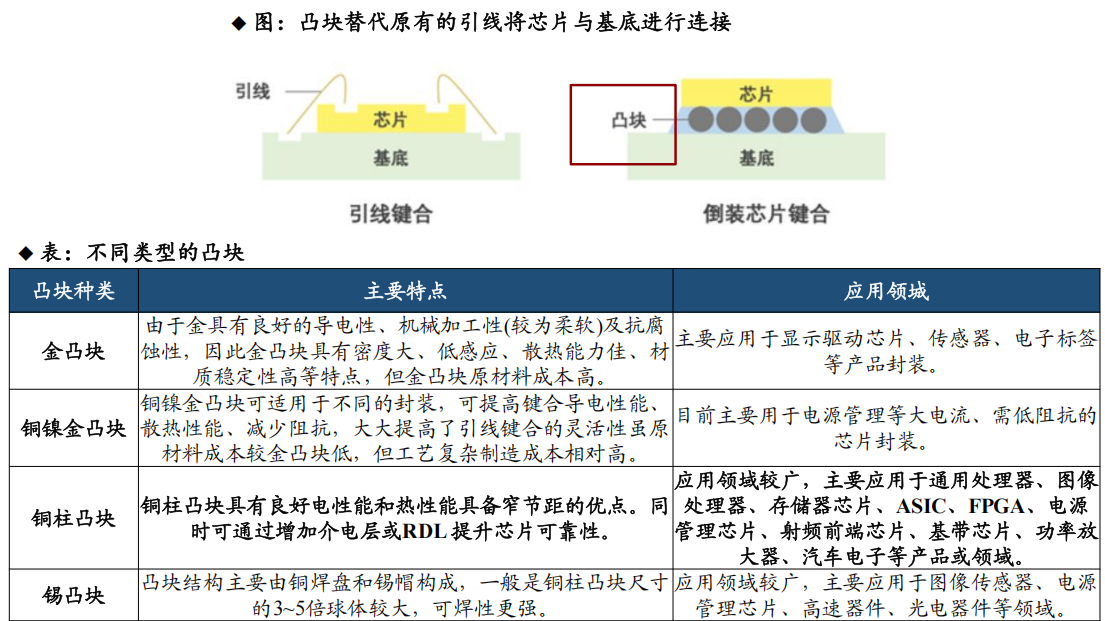

(1)凸块(Bump)

凸块是在芯片表面制作的金属凸起结构,作为芯片与外部电路之间的电气连接“点接口”,广泛应用于倒装芯片(FC)和晶圆级封装(WLP)中。随着技术发展,凸块材料已从早期的金、锡等扩展至铜、铜镍金等多种金属,以适应不同芯片的封装需求。

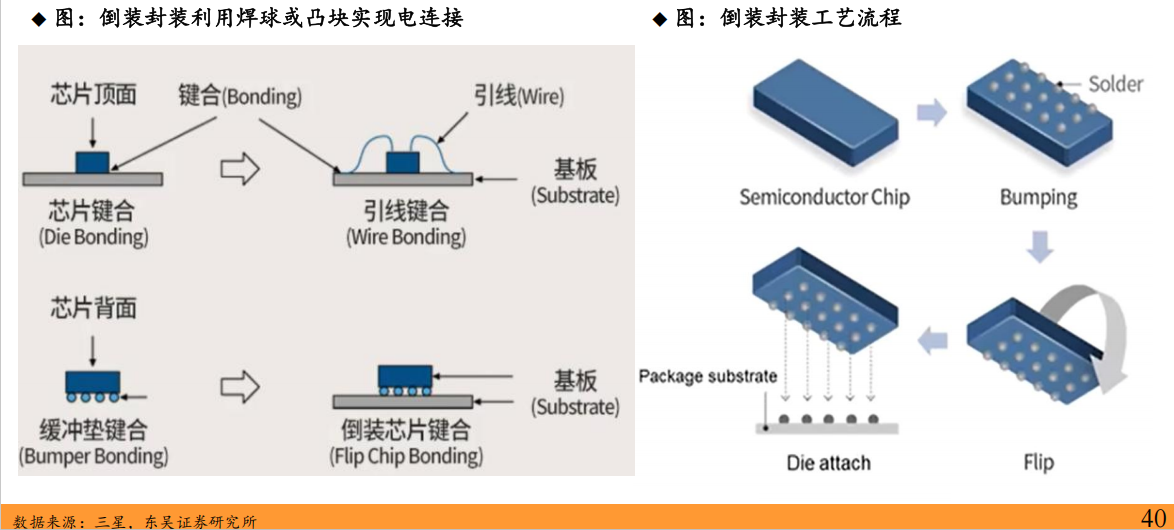

(2)倒装芯片(Flip Chip, FC)

倒装芯片通过将芯片正面朝下直接安装在基板上,利用焊球或凸块实现电气连接,从而实现更紧凑的封装结构。具体工艺是在芯片的I/O焊盘上制作锡铅球,随后将芯片翻转并加热,使焊球与基板焊接。该技术广泛应用于CPU、GPU及芯片组等高性能器件,如常见的CPU和内存条。相较于传统引线键合,FC的I/O端口分布于整个芯片表面,不仅提高了封装密度和处理速度,还可借鉴SMT技术进行高效加工。

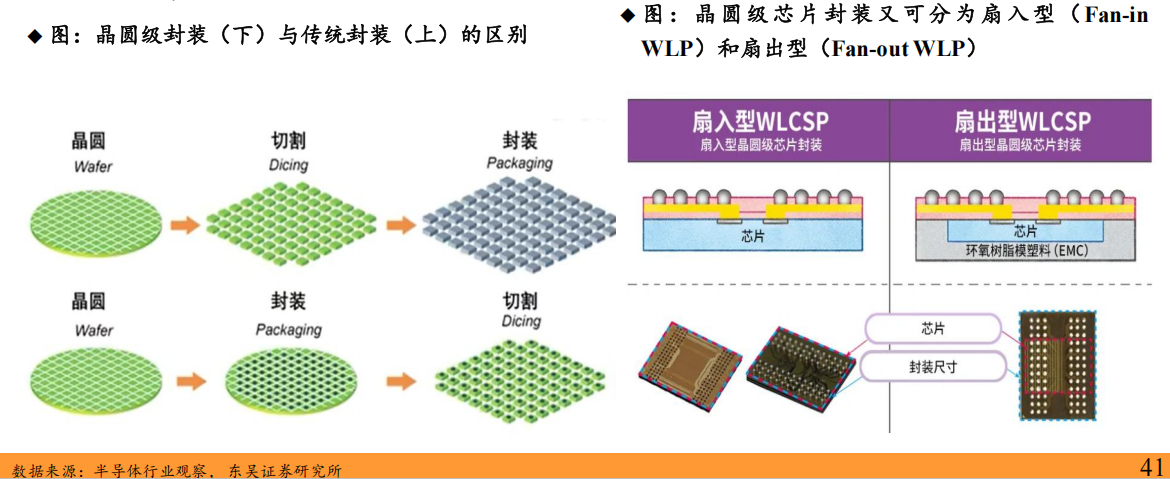

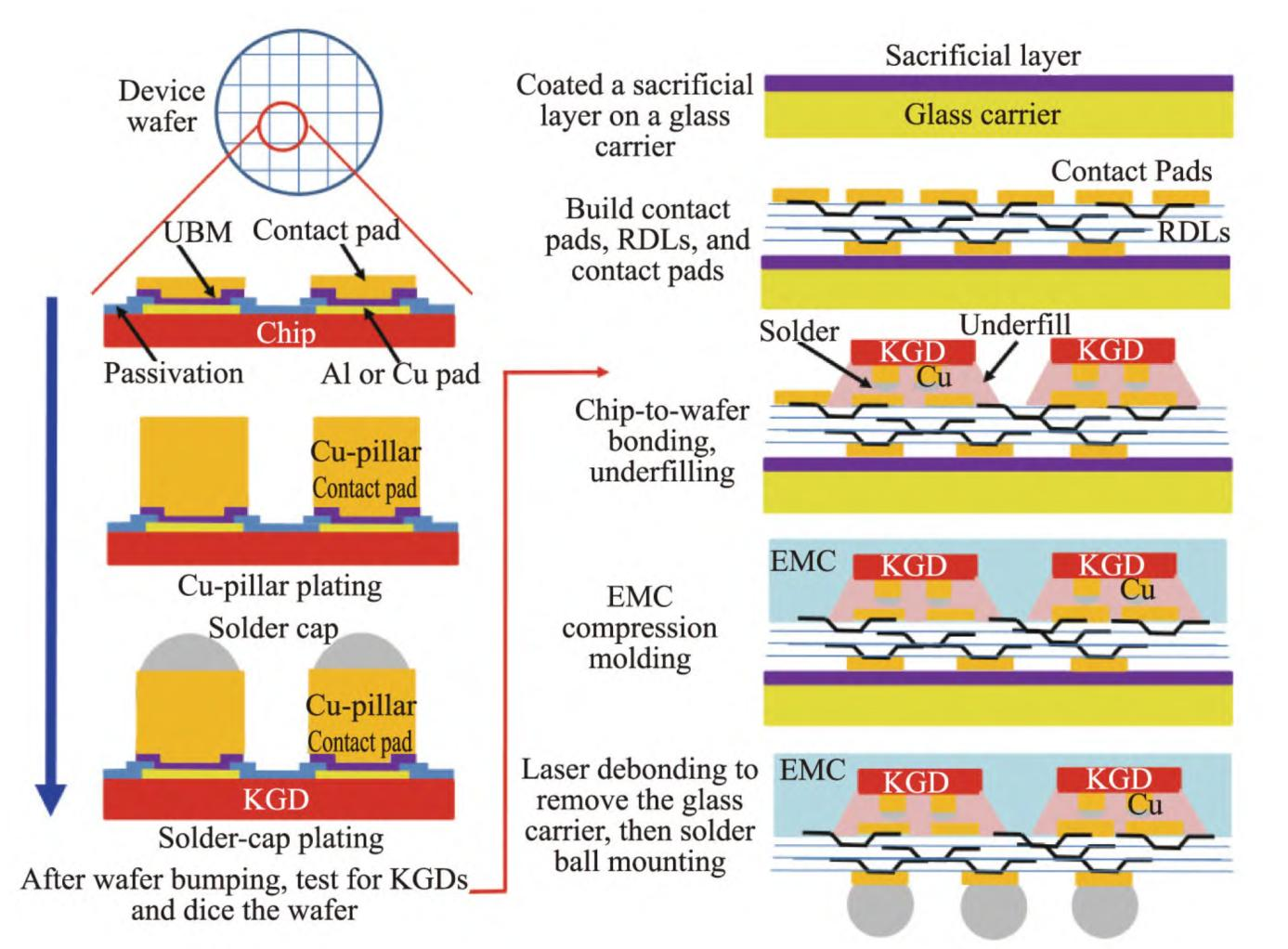

(3)晶圆级封装(Wafer-level Packaging, WLP)

WLP在晶圆阶段即完成封装工序,通过在晶圆顶部或底部添加保护层并形成电路连接,最后切割为单个芯片。WLP主要分为扇入型(Fan-in)和扇出型(Fan-out):扇入型将导线和焊球直接制作在晶圆表面,而扇出型则通过重新排布芯片形成模塑晶圆,其引脚数量更多、封装尺寸更大。扇入型工艺简单、成本较低,适用于大批量生产;扇出型则更适合高I/O数量或复杂设计需求。WLP已广泛用于闪存、DRAM、射频器件、模拟器件等领域。

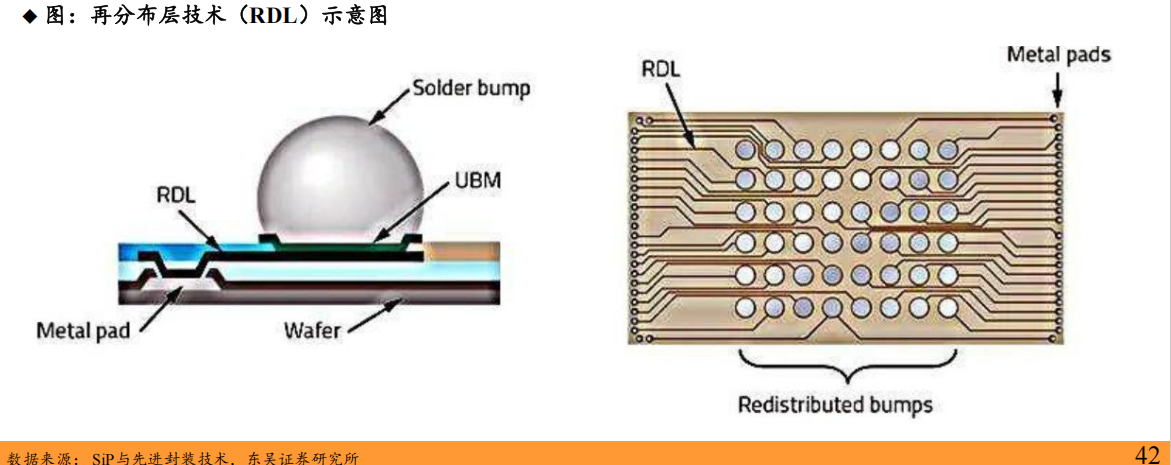

(4)再分布层技术(RDL)

RDL通过在晶圆表面沉积金属层与介质层,形成金属布线,将I/O端口重新布局至更宽松的区域,并实现面阵列排布。传统芯片设计中I/O端口多位于边缘,适合引线键合,但难以满足倒装芯片的要求,RDL技术因此应运而生。在封装过程中,RDL通过重新布线连接芯片与封装基板,有助于实现复杂电路连接、提升性能并缩小封装面积。

在晶圆级封装中,RDL是实现扇入或扇出布局的关键;在2.5D封装中,RDL用于互联硅基板上下方的凸块;在3D封装中,RDL则负责对准上下层芯片的I/O,完成电气连接。

RDL的主要工艺流程包括:①形成钝化绝缘层并开孔;②沉积粘附层与种子层;③光刻显影并电镀形成线路;④去除光刻胶并刻蚀多余层;重复上述步骤完成多层布线。

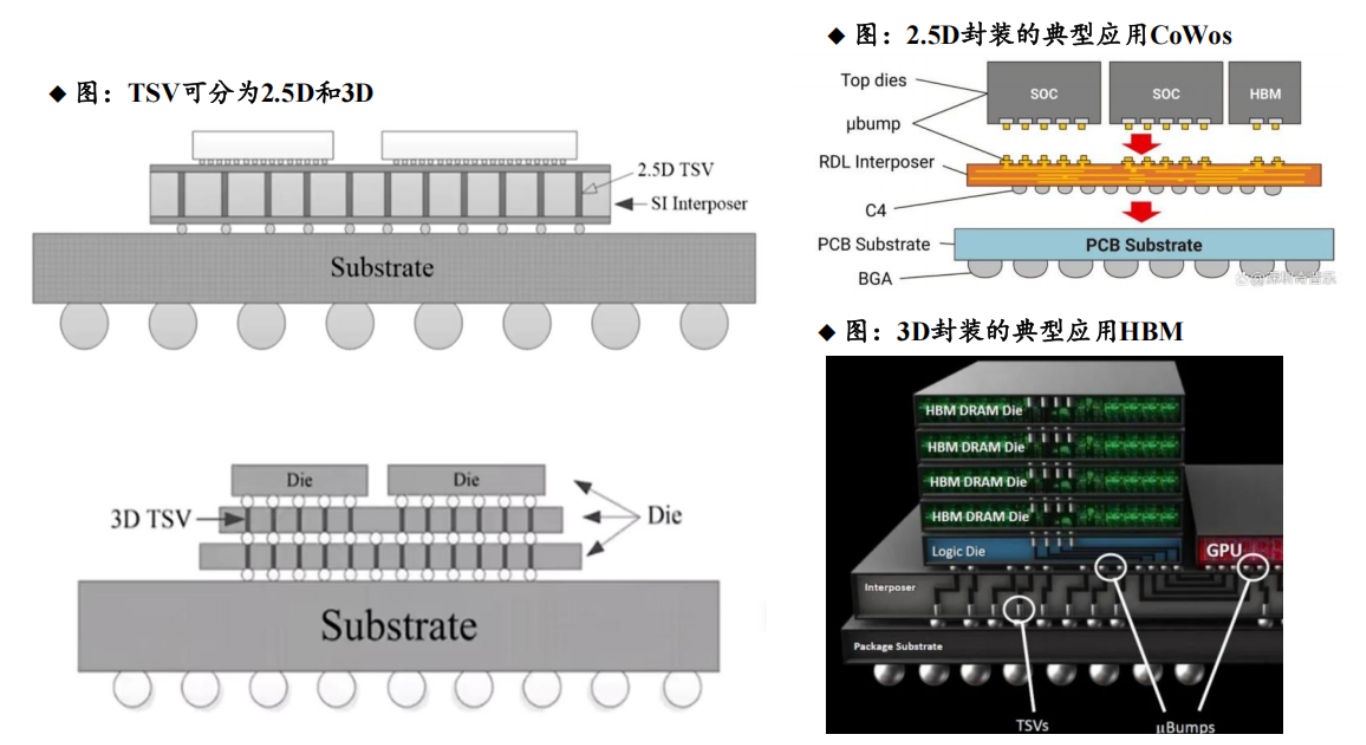

(5)硅通孔技术(TSV)

TSV通过在芯片内部垂直穿透硅片,形成连接芯片顶部与底部的金属通道,实现不同芯片层级之间的电信号传输。TSV可分为2.5D与3D两种类型:2.5D TSV需借助中介层(Interposer),典型代表为台积电的CoWoS技术;3D TSV则无需中介层,已广泛应用于SK海力士和三星的高带宽内存(HBM)产品中。

封装设备的发展与市场需求

传统封装与先进封装在设备类型上有所重叠,如减薄机、划片机、固晶机、键合机、塑封机等均为通用设备,但先进封装对设备性能提出更高要求,例如更薄的晶圆研磨、非引线框架键合、压塑成型工艺等。

2023年,后道封装设备占半导体设备总价值的约5%,其中固晶机、划片机和键合机是核心设备。据SEMI预测,2025年全球封装设备市场规模将达417亿元,固晶机占比30%,划片机占28%,键合机占23%。

键合技术的演进

随着封装形式的演进,键合技术不断追求更小的互联距离以实现更高传输速度。从引线键合、倒装键合、热压键合到混合键合,键合精度从最初的5–10/mm²提升至10k+/mm²,互联距离从20–10µm缩小至0.5–0.1µm,同时每比特能耗也显著降低至0.05 pJ/Bit,满足了对更高集成度、更薄封装和更强性能的需求。