混合键合技术的诞生背景

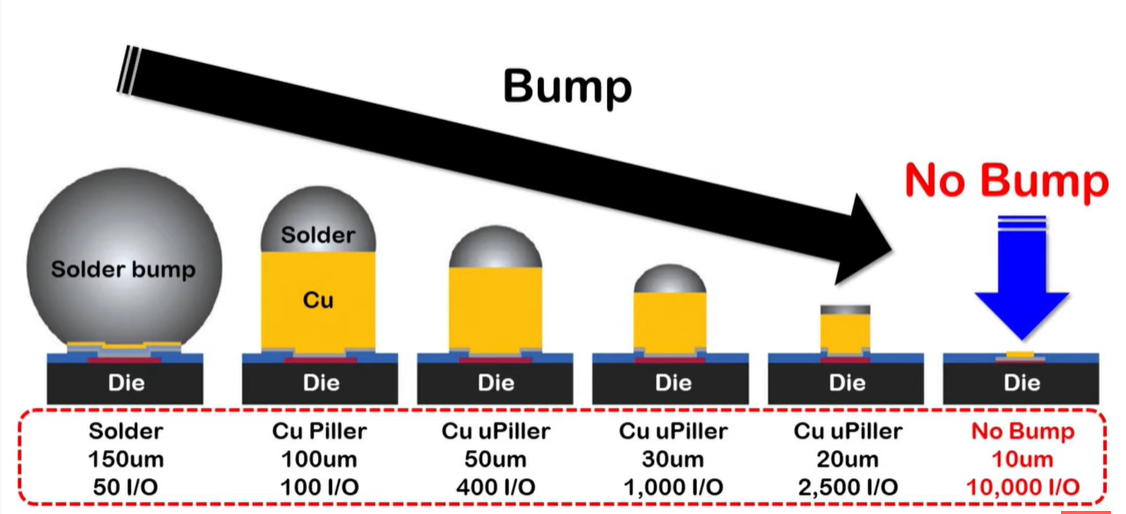

随着半导体工艺节点持续微缩(7nm、5nm、3nm及以下),单纯依靠线宽缩小已逼近物理瓶颈。行业转而通过先进封装技术提升系统性能、能效比与功能集成度。在市场需求驱动下,封装技术历经焊料凸点(Solder Bump)、铜柱凸点(Pillar Bump)-2D、微凸点(Micro Bump)、微焊盘(Micro Pad)-2.5D到无凸点(Bumpless)-3D的演进。混合键合(Hybrid Bonding)正是实现三维集成电路(3D IC) 的关键突破。

混合键合的核心优势

1、异构集成

支持不同工艺节点/功能的芯片(逻辑、高带宽内存、模拟/RF、传感器)以超高密度(互连节距<1μm)、低延迟、高带宽集成。

2、三维堆叠

实现芯片级垂直堆叠(如存储单元堆叠、逻辑层堆叠),建立短距、低寄生电阻电容的互连通道,最大化空间利用率。

3、尺寸优化

构建超薄堆叠结构(厚度<10μm),满足移动/可穿戴设备严苛尺寸要求。

4、能效提升

缩短互连距离并降低寄生效应,显著减少功耗,对AI/数据中心等高算力场景至关重要。

技术发展基础

1、材料键合机制

铜-铜直接键合与介质-介质(SiO₂-SiO₂)键合协同,其中铜热压键合技术奠定金属互连基础。

2、表面处理突破

化学机械抛光(CMP)实现原子级平整度与超洁净表面,保障高良率键合。

3、精密对准技术

亚微米级晶圆/芯片对准精度,确保微焊盘精准匹配。

混合键合制程工艺

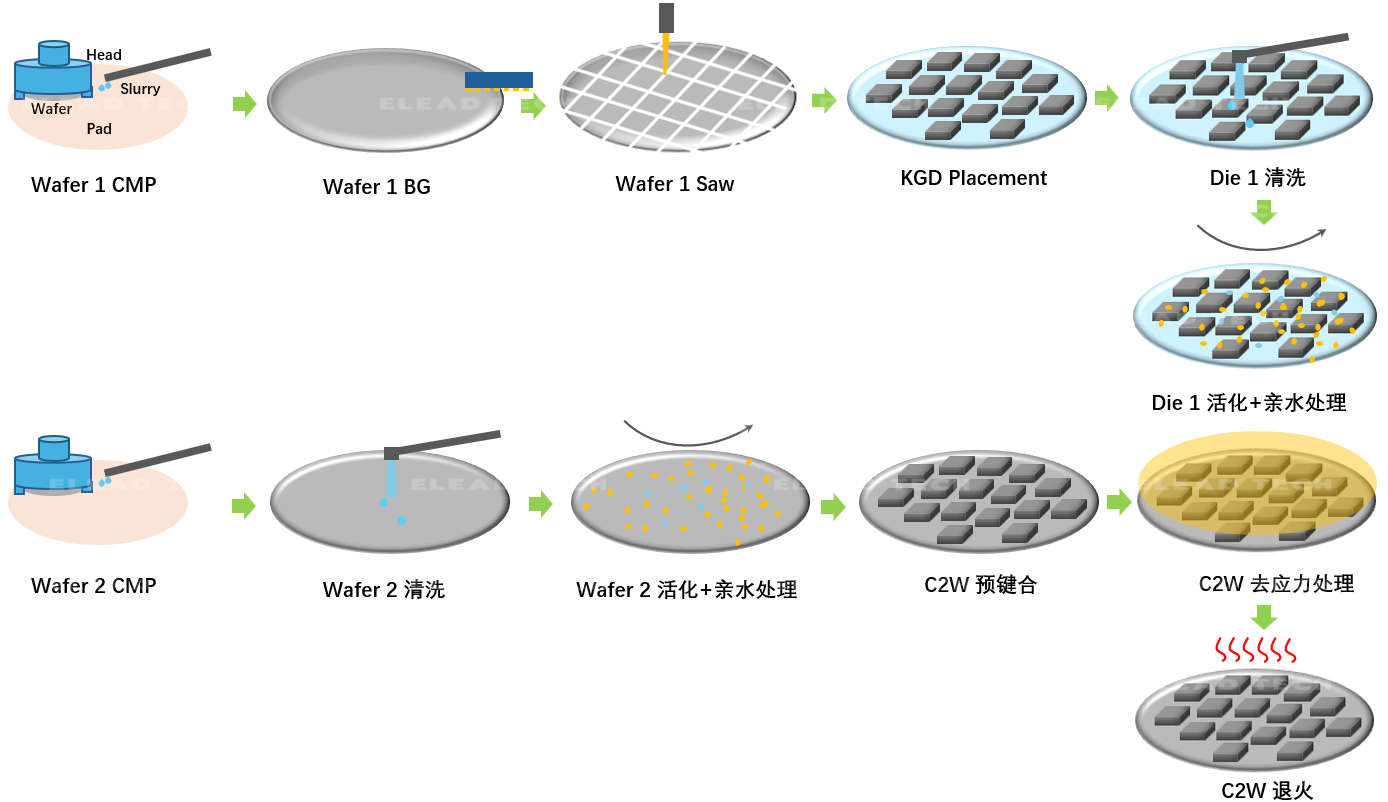

C2W(Chip to Wafer)键合制程前后主要为:

①Wafer 1正面CMP+清洗;

②Wafer 1背面减薄+清洗;

③Wafer 1切单颗(采用激光/等离子切割以减少颗粒污染物);

④KGD-Die1 Placement(PNP分选至蓝膜or 形成重构晶圆);

⑤Wafer 2正面CMP+清洗;

⑥Dier 1 & Wafer 2等离子活化+亲水处理;

⑦Die 1 to Wafer 2常温下对准预键合;

⑧低温热压去应力处理;

⑨高温退火。

从D2W的键合工艺制程来看,允许将不同尺寸、工艺节点的KGD芯片选择性集成到同一晶圆上,从而支持异构集成和定制化设计,避免了不良Die键合导致的良率损失问题降低了整体成本。但其工艺更为复杂,且洁净度更难保障。

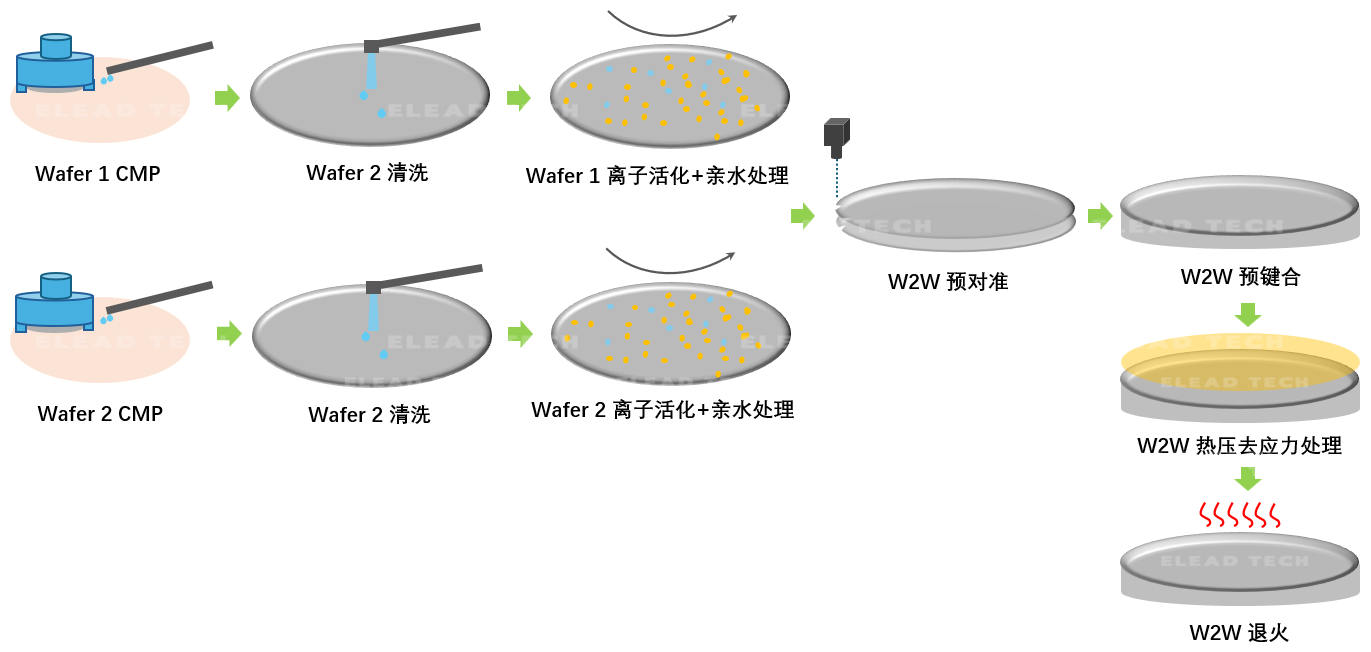

W2W(Wafer to Wafer)键合制程前后主要为:

①Wafer 1正面CMP+清洗;

②Wafer 2正面CMP+清洗;

③Wafer 1 & Wafer 2等离子活化+亲水处理;

④Wafer to Wafer常温下对准预键合;

⑤低温热压去应力处理;

⑥高温退火。

键合工艺相对灵活简便,同时可以提供更高的对准精度、吞吐量和键合良率。但就是无法提前筛选KGD,尤其对于大尺寸的芯片,其良率损失大大增加了产品的成本。

技术难点

D2W的工艺难点:

①晶圆切割成单颗,大大增加了键合界面Particle的风险;

②在KGD分选和预键合时,吸嘴接触拾取和转移芯片时,机械转动而导致Particle增加;

③选择KGD重构晶圆工艺,需要在晶圆背面增加临时键合步骤+解键合以及清洗步骤,工艺不可控风险又增加了;

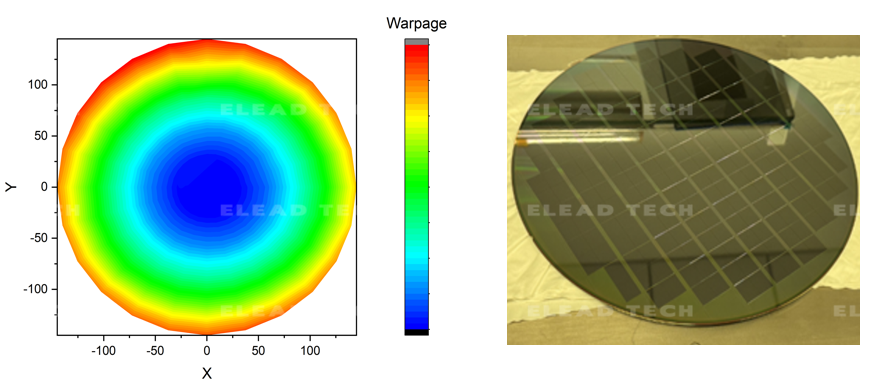

④由于芯片已经薄化,加之在工序转移与预键合拾取过程中的机械转动,芯片的翘曲值,尤其是芯片边缘,有可能会变得更大,这对于预键合步骤是很不利的,会导致介电层之间在对准贴合的时候无法有效接触,退火后产生大空洞,有可能边缘处的Cu Pad也无法形成焊接,最终损失了芯片良率;

⑤室温键合的芯片/晶圆在后续升温时,因材料CTE(热膨胀系数)差异易导致界面开裂。因此,在退火前增加低温去应力步骤非常有必要。考虑到薄化后芯片的机械性能减弱和焊点结构的高密度分布,去应力的处理工艺需要温和且高效。

W2W的工艺难点:晶圆各层材料由于CTE的失配,在历经高温退火时容易发生键合不良(空洞、虚焊等),也需要在退火前增加去应力工艺步骤。

在混合键合(Hybrid Bonding)工艺中,介电层(通常是二氧化硅或低k介质)之间的键合最初主要依靠表面羟基形成的氢键,在室温或低温预键合阶段,维持或施加适当的压力有助于补偿晶圆/芯片因热膨胀系数差异可能产生的微小形变,保持界面大面积的紧密接触,特别是在大尺寸键合或存在翘曲时。

屹立芯创解决方案

针对翘曲与应力难题,屹立芯创应力消除系统SRS通过三重机制优化键合界面:

1. 热力协同调控

o 120℃以下软性气囊施加<0.5MPa垂直压力,直接抑制边缘翘曲,促进应力松弛;

o 热软化效应降低材料屈服强度,促进微米级粗糙表面(Ra<1nm)实现原子级接触;

2. 蠕变应力松弛

o 恒温恒压维持诱导材料蠕变,在短时间内消除内应力,显著降低空洞率;

3. 界面环境控制

o 真空腔室排除水汽,抑制界面空洞形成;

o 平台冷却装置优化降温速率,规避回弹风险。

技术本质:通过"热塑性形变+应力松弛+真空环境"三位一体,重构材料形态稳定性,为后续退火创造原子级接触界面。