芯片组装技术是微组装核心技术之一, 其组装质量直接影响整个器件和组件的性能。随着混合集成电路向着高性能、高密度以及小型化、低成本的方向发展,对芯片的组装技术和可靠性提出了更高的要求。根据芯片种类和应用环境的不同,芯片组装应选用合适的组装技术。芯片组装技术主要有粘接和焊接两种。粘接分为绝缘粘接和导电粘接;焊接则可根据实现方式的不同,分为回流焊接和共晶焊接等。

无论以何种方式来实现芯片的组装,在实际生产中,不可避免会遇到芯片组装失效的情况。

这种类型的分离,一般会在芯片同粘接材料的粘接强度小于粘接材料同底座的粘接强度的情况下发生。发生此类分离的原因可能是粘接材料本身粘接强度不足、粘接工艺缺陷、芯片背面沾污等。

图1 是一例典型的案例,从中可见,粘接材料明显没有与芯片背面产生适当连接,失效因此发生。

这种分离类型一般是在底座同粘接材料之间的粘接强度小于芯片同粘接材料之间的粘接强度的情况下出现的,出现这类分离的原因可能是粘接材料不适应底座材料、粘接工艺缺陷、底座粘接面沾污等。

图2 即为一例典型案例,从中可见,管壳衬底粘接处明显没有粘接材料,失效因此发生。

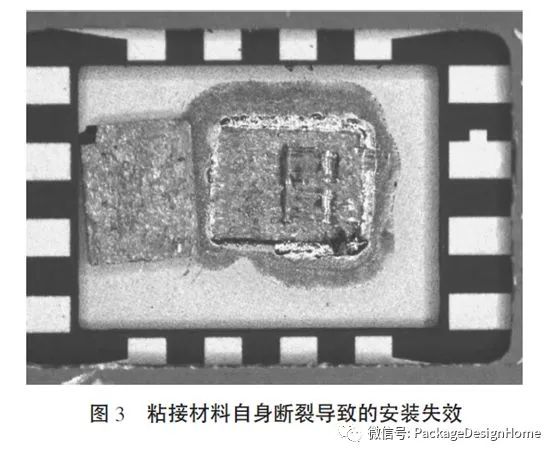

这种类型的分离表现为芯片被剪切掉后,芯片和底座上均保留部分粘接材料,即粘接材料自身内部发生断裂,这是由于粘接材料在焊接工艺过程中受热不均,或自身的质量较差所致。

具体案例如图3所示。

引起胶水气泡的原因一般有两种,其一,在倒入胶水时候,导致空气进入胶水内部,而胶水黏度比较高,使空气无法从中逃脱;其二,调试胶水不均匀,两种就是导致胶水出现气泡最直接的原因。芯片粘接过程中空洞的出现会导致很多问题的出现,最严重,全线无法生产,需要保证粘接效果无气泡也是非常重要的。

如图4示,芯片粘接/贴合产生的空洞。

使用芯片粘接工艺时,应保证粘接界面有良好的洁净度,并在芯片表面施加适当压力。获得良好的表面状态清洁和施加压力都是为了形成界面分子间的结合力。等离子清洗是一种高效的清洁方法。大量资料及试验数据表明,采用微波等离子对被粘接界面进行处理,可达到清洗、活化和刻蚀等处理效果。

如芯片在点银胶前基板上存在污染物,会导致银胶呈圆形形态,此时接触角度大于90°,呈现不润湿的现象,不利于芯片粘接;等离子清洗后,即可使工作表面粗糙度及亲水性大大提高,有利于银胶铺展及芯片粘接。

芯片粘接时采用的固化温度、固化时间与所选用的导电胶型号直接相关,一般型号的导电胶通常有多个推荐的固化条件,在电路允许的温度范围内采用最高温度条件固化,有利于提高粘接质量。同时,提高对粘接芯片施加的压力,也可增加芯片与胶的微观接触面积,进一步提高粘接可靠性。

芯片焊接时除保证焊接表面无污染、表面氧化程度低之外,合理的焊接温度和压力等也是保证焊接质量的重要因素。

焊接温度设置过低或者预热不充分,使得被焊样品没有达到等温状态,可能导致焊料处温度未到达实际熔点以上;焊料熔化不充分,润湿性降低,即形成冷焊点。

焊接温度设置过高,易导致焊料过量溢出,焊接界面之间存留的焊料过薄,降低环境变化及机械应力下的焊接可靠性。适当的焊接压力能增加焊接材料之间的微观接触面积,促进焊料对基体界面的润湿铺展,也有利于排除气泡,减小空洞。

芯片粘接时,会出现空洞和气泡的情况。可通过真空、压力和温度的切换,将气体往除泡机的舱体注入、释放的过程,从而在除泡机舱体内维持较高压力的工作环境。

此时将含有气泡的芯片放入除泡机的舱体内,芯片表面的气泡因为含有残留的空气,此时与除泡机内部的高压环境相作用形成压力差,从而达到将芯片表面的气泡排挤到边缘排出的效果,保证了芯片封装过程中的安全性与稳定性。

随着技术的发展, 芯片的组装方法将会越来越多并且不断完善。半导体器件焊接或粘接的失效,主要与焊接面洁净度或平整度差、氧化物存留、加热不当和基片镀层质量有关。要解决芯片粘接不良问题,必须明确不同焊接与粘接方法的机理, 逐一分析引发失效的相关因素,针对性地从粘接材料、封装工艺实施改进,从而提高芯片组装的可靠性。

根据芯片组装质量分析芯片粘接或焊接情况,可对芯片粘接材料、粘接工艺等加以控制和优化,从而提高组装质量,最大程度地避免组装失效的发生。

屹立芯创 · 除泡品类开创者